Scope

This document describes key hardware aspects of the Ezurio Veda™ IF912 series wireless modules which is a ultra-lower power, single chip connected MCUs with 1x1 Wi-Fi 6 dual band, Bluetooth® Low Energy 5.4, Matter and IP networking. Integrated MCU, Radio, PMU, Flash and PSRAM in 11x7mm size that targeted at Internet-of- Things (IoT) applications for stand-alone operation or to offload a host-processor.

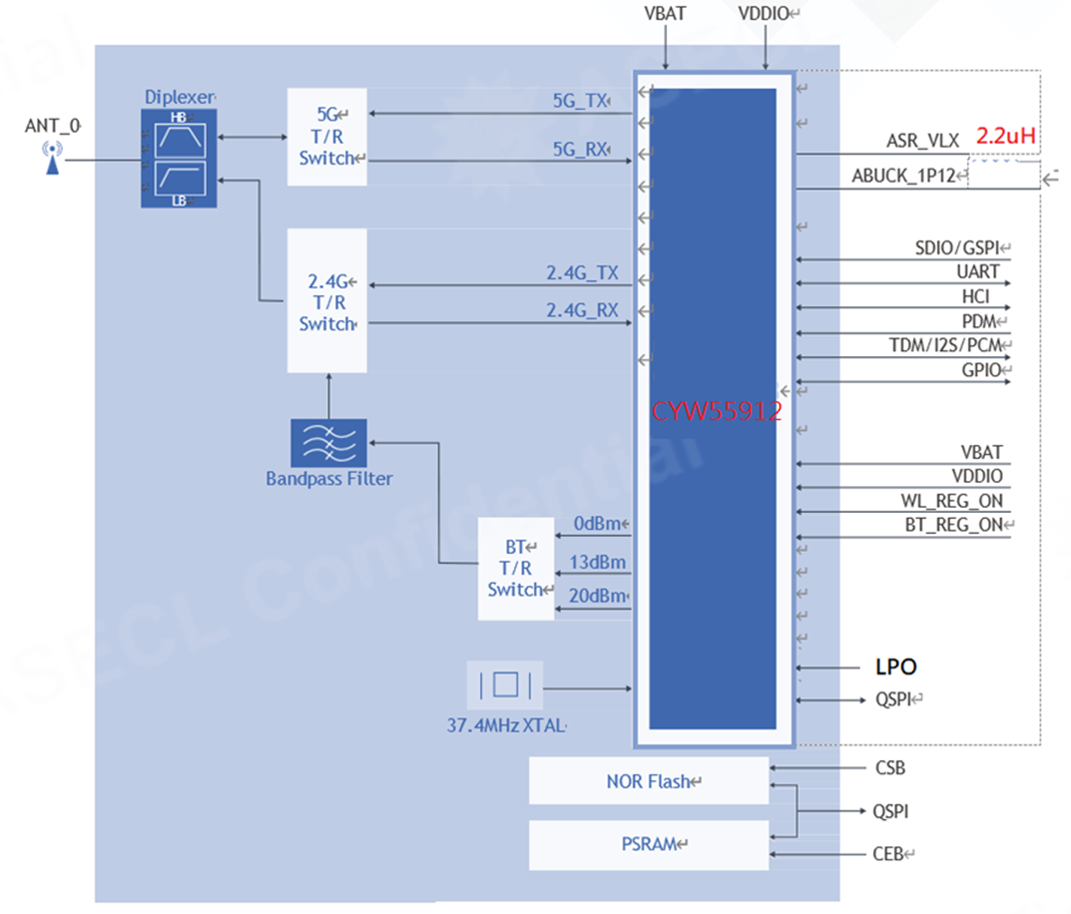

This document is intended to assist device manufacturers and related parties with the integration of this radio into their host devices. Data in this document is drawn from several sources and includes information found in the Infineon CYW55912 Reversion C 2024-10-30 data sheet, along with other documents provided by Infineon.

Note: The information in this document is subject to change. Please contact Ezurio to obtain the most recent version of this document.

Introduction

Overview

The Veda IF912 series wireless module is a highly integrated, small form factor Wi-Fi/Bluetooth module that is optimized for low-power mobile devices.

The Veda IF912 integrated with all WLAN and Bluetooth functionality in a small package supports a low cost and simple implementation. The radio is pre-calibrated and integrates the complete transmit/receive RF paths including bandpass filter, diplexer, switches, reference crystal oscillator, and power management units (PMU). It is available in 7x11x1.4mm solder-down LGA form factors with an RF trace pin out for both Wi-Fi and BT.

A reference certified embedded PCB antenna or the implementation of MHF4 connector for external antennas are available on Veda IF91x DVK, please contact Ezurio for detail information. A list of certified external antennas is shown in Certified Antennas.

Ordering information is listed in Ordering Information. Please contact Ezurio Sales/FAE for further information.

General Description

MCU: 192 MHz Arm® Cortex®-CM33, runs the Wi-Fi and Networking Stacks.

Memory:

- On-Chip memory: 2048-KB ROM and 768-KB RAM. (No Embedded Memory variant)

- Embedded external memory: 8M PSRAM, 8M Flash. (Embedded Memory, 8M PSRAM, 8M Flash variant)

Note: For other embedded memory size, please contact Ezurio.

Wi-Fi:

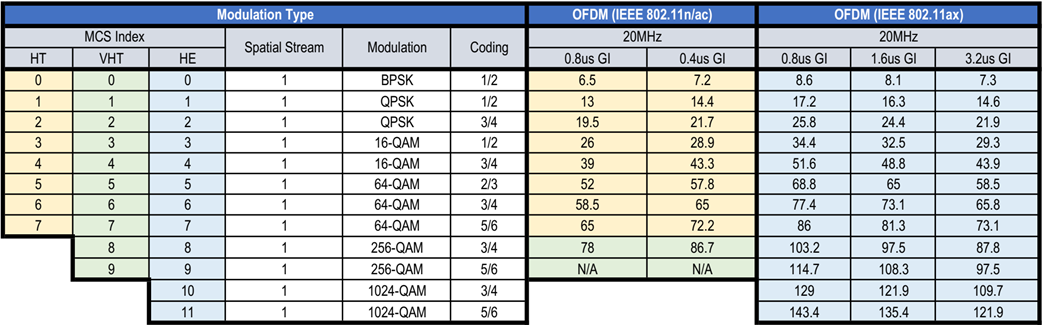

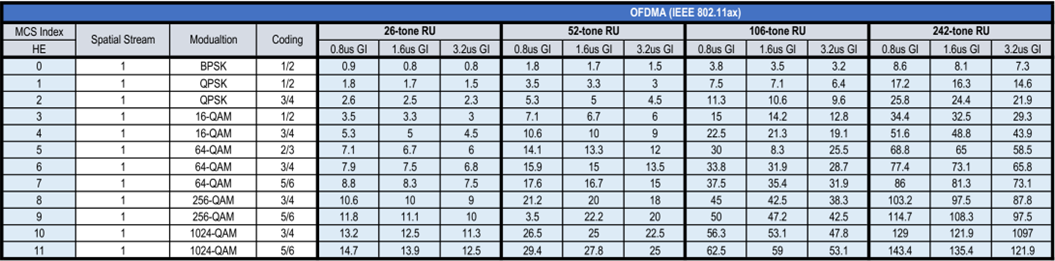

- 1X1, IEEE 802.11a/b/g/n/ac/ax compliant.

- Dual-band (2.4/5GHz), 20 MHz channels supporting PHY data rates up to 802.11ax (MCS11 1024-QAM 5/6).

- Transmit (TX) power with internal PA and LNA.

- Wi-Fi 6 release feature:

- OFDMA uplink and downlink as STA

- Downlink multi-user MIMO as STA

- Individual target-wake-time (TWT)

Bluetooth®:

- Bluetooth® 5.4 (Bluetooth® Low Energy)

- Advertising Coding Selection

- Encrypted Advertising Data

- LE Generic Attribute Profile (GATT) Security Levels Characteristic

- Bluetooth® Low Energy 5.0/5.1/5.2/5.3 features

- LE long range

- LE 2 Mbps

- LE mesh

- Advertising extensions

Security:

- Arm® Trustzone Cryptocell 312

- Life cycle management

- Crypto key establishment and management Crypto offloads

- Secure boot

- Wi-Fi and Bluetooth® independent firmware authentication

- Firmware encryption

- Attestation

- Anti-rollback prevention

This datasheet is subject to change. Please contact Ezurio for further information.

Specification Summary

Processor / SoC / Chipset

| Wireless | Infineon AIROC™ CYW55912 |

Wi-Fi

| Standards | IEEE 802.11ax, 11ac, 11ac, 11a/b/g/n, 11d/h, 11i, 11r, 11w, 11e, 11k, 11ai, 11v | ||||||||||||||

| Wi-Fi Features | Advanced WLAN:

| ||||||||||||||

| Spatial Streams | 1 (1x1 MU-MIMO) | ||||||||||||||

| Supported Data Rates | Support 802.11 ax/ac/a/b/g/n 1x1 MU-MIMO.

| ||||||||||||||

| Max Transmit Power | Up to +19 dBm | ||||||||||||||

| Min Transmit Power | Down to +10.5 dBm | ||||||||||||||

| Modulation Schemes | BPSK, QPSK, CCK, 16-QAM, 64-QAM, 256-QAM, 1024-QAM (See Note) |

Bluetooth

| Standards |

|

| Bluetooth Features | Bluetooth 5.4:

Bluetooth® Low Energy 5.0/5.1/5.2/5.3:

Low power consumption improves battery life of IoT and embedded devices |

| Interface | Host controller interface (HCI) using a high speed UART and PCM/I2S for audio data |

| Bluetooth LE Modulation | GFSK @ 1, 2 Mbps GFSK @ 125, 500 Kbps |

Radio Details

| Features |

One buck regulator, multiple LDO regulators, and a power management unit (PMU) are integrated into the Veda IF913. All regulators are programmable via the PMU. These blocks simplify power supply design for Bluetooth and WLAN functions in embedded designs. | ||||||||||||||||||||||||||

| Pre-Calibration | RF system tested and calibrated in production | ||||||||||||||||||||||||||

| Sleep Clock | Internal low-power oscillator accuracy is only adequate for WLAN, and not for Bluetooth®, if low power for Bluetooth®Low-Energy required. External 32.768 KHz sleep clock is required for Bluetooth® Low Energy to support low power mode. The 32.768 kHz precision oscillator which meets the requirements listed following table must be used.

| ||||||||||||||||||||||||||

| Network Architecture Type | Infrastructure (client operation) |

Radio Performance

| Tx Power | Note: Transmit power on each channel varies per individual country regulations. All values are nominal with +/-2 dBm tolerance at room temperature. Note: HT20/VHT20/HE20 – 20 MHz-wide channels 802.11a

802.11b

802.11g

802.11n (2.4 GHz)

802.11n (5 GHz)

802.11ac (5 GHz)

Bluetooth

| ||||||||||||||||||||||||||||||||||||||||

| RX Sensitivity | (PER <= 10%) All values nominal, +/-2 dBm. 802.11a:

802.11b:

802.11g:

802.11n (2.4 GHz)

802.11n (5 GHz)

802.11ac (5 GHz)

Bluetooth:

| ||||||||||||||||||||||||||||||||||||||||

| Antenna Options | |||||||||||||||||||||||||||||||||||||||||

| 2.4 GHz Frequency Bands |

| ||||||||||||||||||||||||||||||||||||||||

| 5 GHz Frequency Bands | EU

FCC

ISED

UKCA

MIC

RCM

| ||||||||||||||||||||||||||||||||||||||||

| 6 GHz Frequency Bands | Complete / remove as needed | ||||||||||||||||||||||||||||||||||||||||

| Miscellaneous | |||||||||||||||||||||||||||||||||||||||||

Interfaces

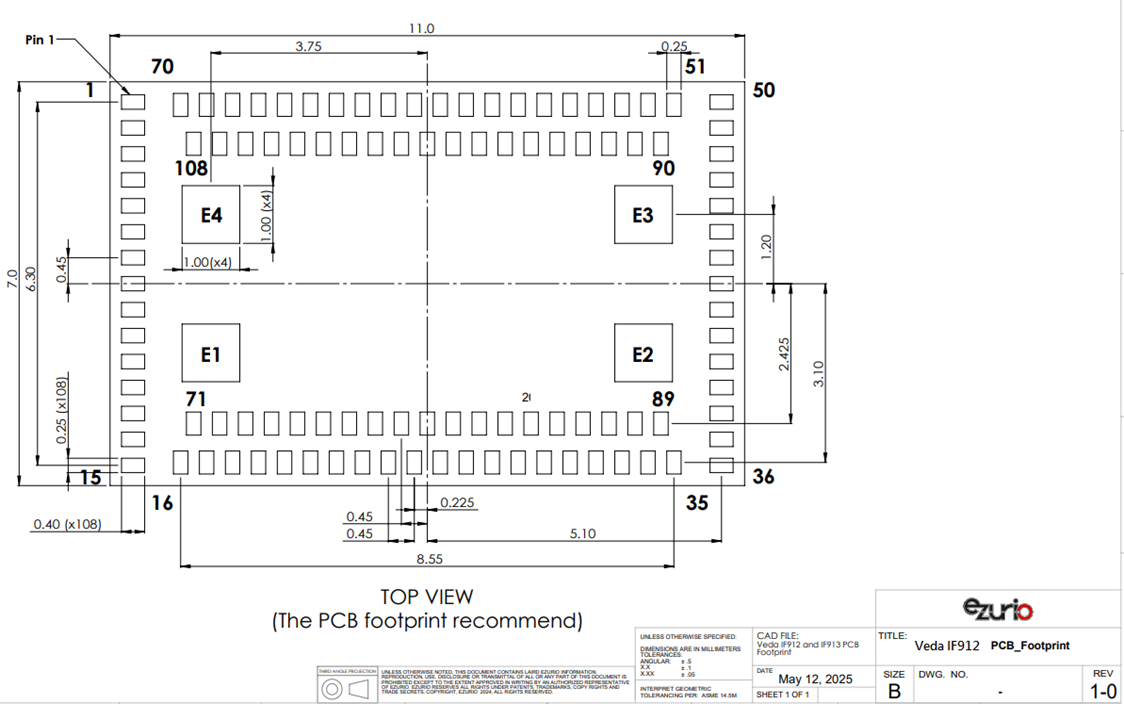

| Physical Interfaces | 108-pin LGA package |

| Network Interfaces | Wi-Fi: SDIO 2.0 (1.8V only) Bluetooth: HCI with HS-UART and PCM/I2S |

Power

| Input Voltage | Typical DC 3.3 V, operating range from DC 3.13V to 4.8V |

| I/O Signal Voltage | Typical DC 1.8 V ± 5% |

Mechanical

| Dimensions | 11x7x1.4mm |

| Weight | TBD |

Software

| OS Support | ThreadX RTOS NetX Secure TLS 1.3 NetX Duo (TCP/IP) |

| Security | WPA, WPA2 (Enterprise) and WPA3 (Enterprise) support for powerful encryption and authentication |

| Operating Modes | |

| Firmware Update |

Environmental

| Operating Temperature | -40° to +85°C (-40° to +185°F) |

| Storage Temperature | -40° to +85°C (-40° to +185°F) |

| Operating Humidity | <85% (non-condensing) |

| Storage Humidity | 5 to 95% (non-condensing) |

| MSL (Moisture Sensitivity Level) | 4 |

| Maximum Electrostatic Discharge | Conductive 8KV; Air coupled 12KV (follows EN61000-4-2) |

| Lead Free | Lead-free and RoHS Compliant |

Certifications

| Regulatory Compliance |

| ||||||||||||

| Compliance Standards |

| ||||||||||||

| Bluetooth SIG | Bluetooth® SIG Qualification TBD  | ||||||||||||

Development

| Development Kit | 453-00396-K1 - Development Kit, Module, Veda IF912, SIP, Dual Band, No Memory, RF Trace Pin |

Hardware Architecture

Block Diagrams

Note: For embedded memory variant, please connect the QSPI bus outside the SIP. See Veda IF912 Implementation Details.

Pin-Out / Package Layout

| Pin # | Name | Type | Voltage Ref. | Function | Main Chip Pin out | If Not Used |

|---|---|---|---|---|---|---|

| 1 | GND | - | - | Ground | - | GND |

| 2 | TDM1_MCK | I/O | VDDIO | TDM1 Interface Master Clock / I2S Master Clock / PCM interface | E2 | NC |

| 3 | GND | - | - | Ground | - | GND |

| 4 | TDM1_SCK | I/O | VDDIO | TDM1 Interface Slave Clock / I2S Interface Clock / PCM interface | E3 | NC |

| 5 | GND | - | - | Ground | - | GND |

| 6 | TDM1_WS | I/O | VDDIO | TDM1 Interface Word Select / I2S Interface Word Select / PCM interface | D3 | NC |

| 7 | TDM1_DO | I/O | VDDIO | TDM1 Interface Data Out / I2S Interface Data Out / PCM interface | F3 | NC |

| 8 | TDM1_DI | I/O | VDDIO | TDM1 Interface Data In / I2S Interface Data In / PCM interface | D4 | NC |

| 9 | BT_DEV_WAKE | I | VDDIO | Bluetooth Device Wake-up | J3 | NC |

| 10 | WL_DEV_WAKE | I | VDDIO | WLAN Device Wake-up / Programmable General purpose I/O | J2 | NC |

| 11 | BT_HOST_WAKE | O | VDDIO | Host wake up | F2 | NC |

| 12 | GND | - | - | Ground | - | GND |

| 13 | DIP_OUT | RF | - | WIFI+BT RF output port 0 | - | 50 ohm terminated |

| 14 | GND | - | - | Ground | - | GND |

| 15 | GND | - | - | Ground | - | GND |

| 16 | LHL_GPIO_8 | I/O | VDDIO | Miscellaneous general purpose GPIO_8 | G2 | NC |

| 17 | LHL_GPIO_9 | I/O | VDDIO | Miscellaneous general purpose GPIO_9 | H1 | NC |

| 18 | LHL_GPIO_3 | I/O | VDDIO | Miscellaneous general purpose GPIO_3 | H5 | NC |

| 19 | LHL_GPIO_5 | I/O | VDDIO | Miscellaneous general purpose GPIO_5 | H3 | NC |

| 20 | GND | - | - | Ground | - | GND |

| 21 | LPO_IN | I | VDDIO | External sleep clock input (32.768 KHz) Note: Needed for Bluetooth® Low Energy to support low power mode. | J5 | - |

| 22 | GND | - | - | Ground | - | GND |

| 23 | WL_HOST_WAKE | O | VDDIO | WLAN HOST WAKE / Programmable General purpose I/O | G10 | NC |

| 24 | BT_UART_TXD | O | VDDIO | UART Serial Output. Serial data output for the HCI UART interface. | F7 | NC |

| 25 | GND | - | - | Ground | - | GND |

| 26 | ABUCK_1P12 | PWR input | - | Normal 1.12V power input and 0.74V when in sleep mode. Please connect to the filtered ABUCK voltage. See pin-33 and pin-34. | B8 | - |

| 27 | ABUCK_1P12 | PWR input | - | - | ||

| 28 | GND | - | - | Ground | - | GND |

| 29 | TDM2_MCK | I/O | VDDIO | TDM2 Interface Master Clock / I2S Master Clock/ PCM interface | B1 | NC |

| 30 | GND | - | - | Ground | - | GND |

| 31 | TDM2_SCK | I/O | VDDIO | TDM2 Interface Slave Clock / I2S Interface Clock / PCM interface | A1 | NC |

| 32 | GND | - | - | Ground | - | GND |

| 33 | ASR_VLX | PWR output | - | Analog Switching Regulator (ABUCK) power stage output. Please connect to external L-C Filter (2.2uH+ 4.7uF) and connected to ABUCK_1P12 (pin-26; pin-27) See Veda IF912 Implementation Details | A10 | - |

| 34 | ASR_VLX | PWR output | - | - | ||

| 35 | GND | - | - | Ground | GND | |

| 36 | GND | - | - | Ground | - | GND |

| 37 | VBAT | PWR | 3.3V | Main DC supply voltage for module. Operational: VBAT is 3.0V to 4.8V

| B10/C10/D10 | - |

| 38 | VBAT | PWR | 3.3V | - | ||

| 39 | GND | - | - | Ground | - | GND |

| 40 | SDIO_CLK | I | VDDIO | SDIO Clock Input / gSPI Clock Interface | A7 | NC |

| 41 | GND | - | - | Ground | - | GND |

| 42 | SDIO_CMD | I/O | VDDIO | SDIO Command Line/ gSPI MOSI Interface | A6 | NC |

| 43 | SDIO_DATA_0 | I/O | VDDIO | SDIO Data line 0/ gSPI MISO Interface | B6 | NC |

| 44 | SDIO_DATA_1 | I/O | VDDIO | SDIO Data line 1/ gSPI interrupt Interface | B7 | NC |

| 45 | SDIO_DATA_2 | I/O | VDDIO | SDIO Data line 2/ gSPI Interface This pin is also used for strapping option for SDIO or gSPI. Default pull during strapping=”H” for SDIO bus; pull it “L” during strapping for gSPI bus. | C7 | NC |

| 46 | SDIO_DATA_3 | I/O | VDDIO | SDIO Data line 3/ gSPI CS Interface | C6 | NC |

| 47 | GND | - | - | Ground | - | GND |

| 48 | SCLK | I/O | VDDIO | Serial Clock input for embedded memory. For No embedded memory variant, keep this pin NC. | - | NC |

| 49 | GND | - | - | Ground | - | GND |

| 50 | SI | I/O | VDDIO | Serial Data Input / Serial Data Input Output 0 for embedded memory. For No embedded memory variant, keep this pin NC. | - | NC |

| 51 | SIO2 | I/O | VDDIO | Serial Data Input / Serial Data Input Output 2 for embedded memory. For No embedded memory variant, keep this pin NC. | - | NC |

| 52 | SIO1 | I/O | VDDIO | Serial Data Input / Serial Data Input Output 1 for embedded memory. For No embedded memory variant, keep this pin NC. | - | NC |

| 53 | HOLDB | I/O | VDDIO | Hold Input/Serial Data Input Output 3 for embedded memory. For No embedded memory variant, keep this pin NC. | - | NC |

| 54 | CEB | I | VDDIO | Chip Select input, active low (CE pin for embedded PSRAM) For No embedded memory variant, keep this pin NC. | - | NC |

| 55 | CSB | I | VDDIO | Chip Select input, active low (CS pin for embedded NOR Flash) For No embedded memory variant, keep this pin NC. | - | NC |

| 56 | SMIF_SPHB_DQ0 | I/O | VDDIO |

| A4 | NC |

| 57 | SMIF_SPHB_DQ1 | I/O | VDDIO | SMIF data line 1.

| B4 | NC |

| 58 | GND | - | - | Ground | - | GND |

| 59 | VDDIO | PWR input | - | 1.8 V IO supply for WLAN GPIOs

| D6 | NC |

| 60 | BT_GPIO_0 | I/O | VDDIO | Bluetooth® general purpose I/O | F1 | NC |

| 61 | BT_GPIO_7 | I/O | VDDIO | Bluetooth® general purpose I/O | A3 | NC |

| 62 | BT_GPIO_16 | I/O | VDDIO | Bluetooth® general purpose I/O | B3 | NC |

| 63 | BT_GPIO_17 | I/O | VDDIO | Bluetooth® general purpose I/O | C3 | NC |

| 64 | BT_GPIO_5 | I/O | VDDIO | Bluetooth® general purpose I/O | D7 | NC |

| 65 | BT_GPIO_6 | I/O | VDDIO | Bluetooth® general purpose I/O | E6 | NC |

| 66 | BT_GPIO_3 | I/O | VDDIO | Bluetooth® general purpose I/O | E5 | NC |

| 67 | BT_GPIO_4 | I/O | VDDIO | Bluetooth® general purpose I/O | F5 | NC |

| 68 | BT_GPIO_2 | I/O | VDDIO | Bluetooth® general purpose I/O | E4 | NC |

| 69 | GND | - | - | Ground | - | GND |

| 70 | DMIC_DATA | I/O | VDDIO | Digital mic data | E1 | NC |

| 71 | GND | - | - | Ground | - | GND |

| 72 | LHL_GPIO_4 | I/O | VDDIO | Miscellaneous general purpose GPIO_4 | H4 | NC |

| 73 | LHL_GPIO_2 | I/O | VDDIO | Miscellaneous general purpose GPIO_2 | H6 | NC |

| 74 | LHL_GPIO_6 | I/O | VDDIO | Miscellaneous general purpose GPIO_6 | G1 | NC |

| 75 | GND | - | - | Ground | - | GND |

| 76 | GND | - | - | Ground | - | GND |

| 77 | MIC_P | I | VDDIO | ADC microphone positive input | E8 | NC |

| 78 | GND | - | - | Ground | - | GND |

| 79 | BT_UART_RXD | I | VDDIO | UART Serial Input. Serial data input for the HCI UART interface. | G6 | NC |

| 80 | BT_UART_RTS_N | O | VDDIO | UART request-to-send. Active-low request-to-send signal for the HCI UART interface. Bluetooth® LED control pin. | G7 | NC |

| 81 | BT_UART_CTS_N | I | VDDIO | UART clear-to-send. Active-low clear-to-send signal for the HCI UART interface. | F6 | NC |

| 82 | BT_REG_ON | I | VDDIO | Used by the PMU to power up or power down the internal regulators used by the Bluetooth® section. When deasserted, this pin holds the Bluetooth® section in reset. This pin has an internal 50 kΩ pull-down resistor by default. that is auto enabled/disabled by programming. | C8 | - |

| 83 | WL_REG_ON | I | VDDIO | Not used for IF913/IF912. This should be tied to GND on board. | A8 | GND |

| 84~86 | GND | - | - | Ground | - | GND |

| 87 | TDM2_DI | I/O | VDDIO | TDM2 Interface Data In / I2S Interface Data In / PCM interface | D2 | NC |

| 88 | TDM2_DO | I/O | VDDIO | TDM2 Interface Data Out / I2S Interface Data Out / PCM interface | C1 | NC |

| 89 | TDM2_WS | I/O | VDDIO | TDM2 Interface Word Select / I2S Interface Word Select / PCM interface | A2 | NC |

| 90 | VCC | PWR | - | Memory 1.8V power supply | - | - |

| 91 | GND | - | - | Ground | - | GND |

| 92 | SMIF_SPHB_CLK | O | VDDIO | SMIF clock output

| A5 | GND |

| 93 | GND | - | - | Ground | - | GND |

| 94 | SMIF_SPHB_DQ2 | I/O | VDDIO | SMIF data line 2.

| B5 | - |

| 95 | SMIF_SPHB_DQ3 | I/O | VDDIO | SMIF data line 3.

| C5 | NC |

| 96 | SMIF_SPHB_ CS0_N | O | VDDIO | SMIF chip select0 active-low output

| C4 | NC |

| 97 | SMIF_SPHB_ CS1_N | O | VDDIO | SMIF chip select1 active-low output

| G3 | NC |

| 98~107 | GND | - | - | Ground | - | GND |

| 108 | DMIC_CLK | I/O | VDDIO | Digital mic clock | D1 | NC |

| E1~E4 | GND | - | - | Ground | GND |

Mechanical Drawings

Veda IF912 SIP package is 11 x 7 x 1.4 mm.

Note:

Dimensions are in millimeters tolerances:

Angular: ± 0.5

X.X: ± 0.1

X.XX: ± 0.05

Integration Guidelines

Antenna Integration

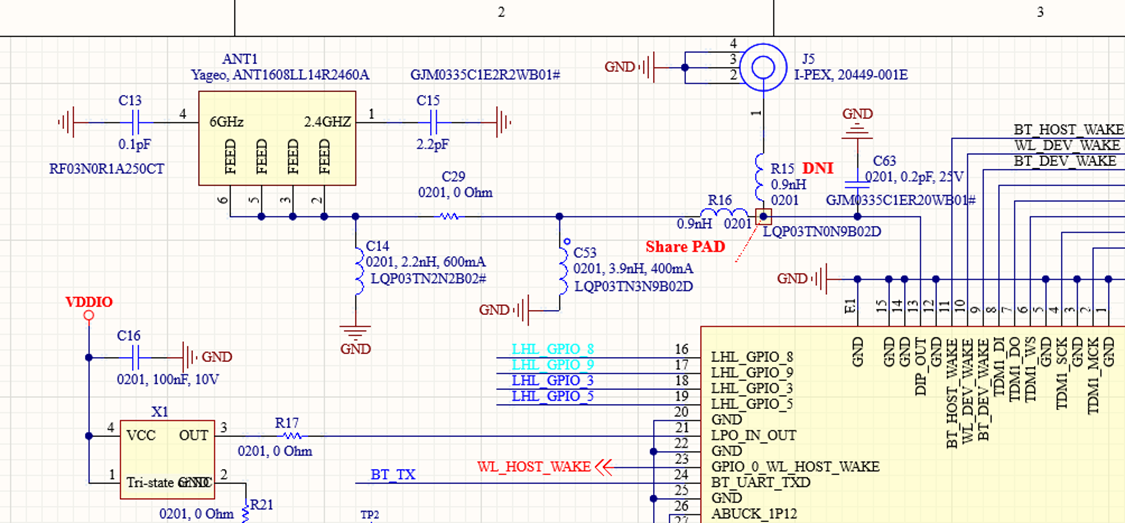

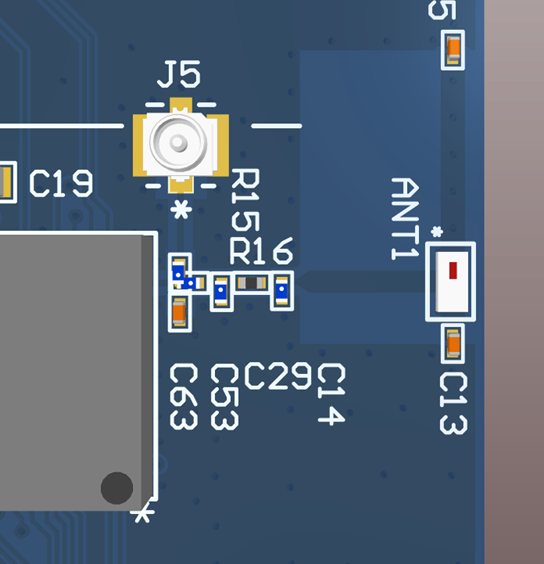

MHF4 and Embedded PCB antenna

The Veda IF912 DVK design has two antenna connection options which are MHF4 and embedded PCB antenna. Pop on R15, users can get the RF signal out at MHF4 connector for external antenna. Pop on R16 will allow users to use the embedded PCB antenna.

Please copy the components’ location for the RF trace from the DVK to maintain the RF performance and adopt Ezurio certification grant.

Certified Antennas

The Veda IF912 module was tested with antennas listed in the following table. The OEM can choose a different manufacturer’s antenna but must make sure it is of same type and that the gain is less than or equal to the antenna that is approved for use.

| Manufacturer | Model | Ezurio Part Number | Type | Connector | Peak Gain (dBi) at 2.4GHz | Peak Gain (dBi) at 5GHz | Peak Gain (dBi) at 6GHz |

|---|---|---|---|---|---|---|---|

| Ezurio (formerly Laird Connectivity) | FlexMIMO 6E | EFD2471A3S-10MH4L | PIFA | MHF4L | 2.2 | 3.8 | 3.3 |

| Ezurio (formerly Laird Connectivity) | FlexPIFA 6E | EFB2471A3S-10MH4L | PIFA | MHF4L | 2.2 | 3.9 | 3.8 |

| Ezurio (formerly Laird Connectivity) | Mini NanoBlade Flex 6 GHz | EMF2471A3S-10MH4L | PCB Dipole | MHF4L | 2.4 | 4.4 | 5.2 |

| Joymax Electronics | Dipole 6E | TWX-100BRSAX-2001 / TWX-100BRS3B | Dipole | RP-SMA | 2 | 4.0 | 4.0 |

Host Platform Implementation Details

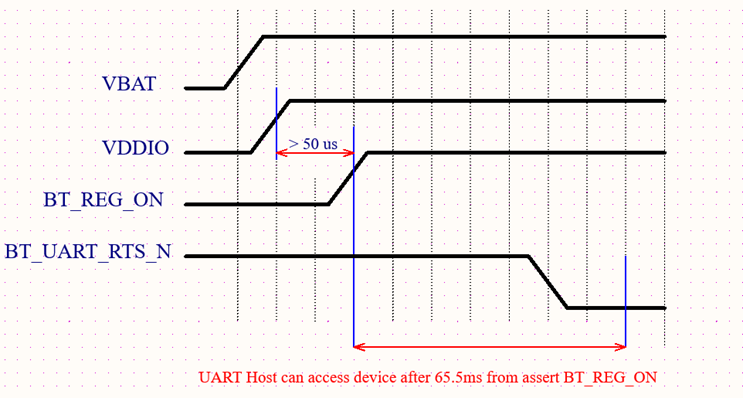

Power-Up Sequence and Timing

To maintain stable MCU and Bluetooth starting up, below power up sequency timing is required.

- VBAT and VDDIO should not rise 10%–90% faster than 40 microseconds.

- VBAT should be up before or at the same time as VDDIO. VDDIO should NOT be present first or be held high before VBAT is high.

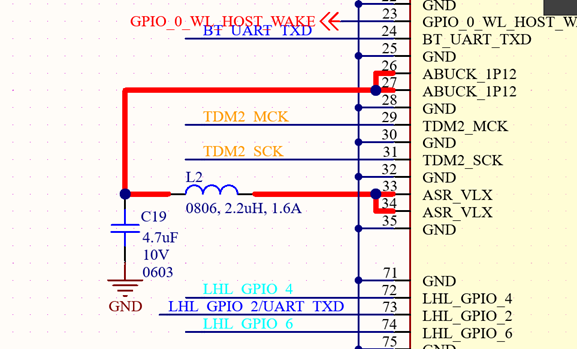

L-C filter for Buck switching regulator

An Analog Switching Regulator (ASR or ABUCK) is built in the Veda IF912 module, the ABUCK output is brought out to pin-33 and pin-34. A L-C filter (2.2uH and 4.7uF) is required to filter out the switching noise before it feeds into ABUCK_1P12 (pin-26 and pin-27). Keep the 2.2uH and 4.7uF as close to Veda IF913 as possible to keep the current flow loop small as you can. Please refer to the Ezurio DVK for the detail placement and routing. Detail parts information is shown in below.

- 2.2uH: 74479276222C (Wurth Elektronik)

- 4.7uF: GRM188C71A475KE11# (Murata)

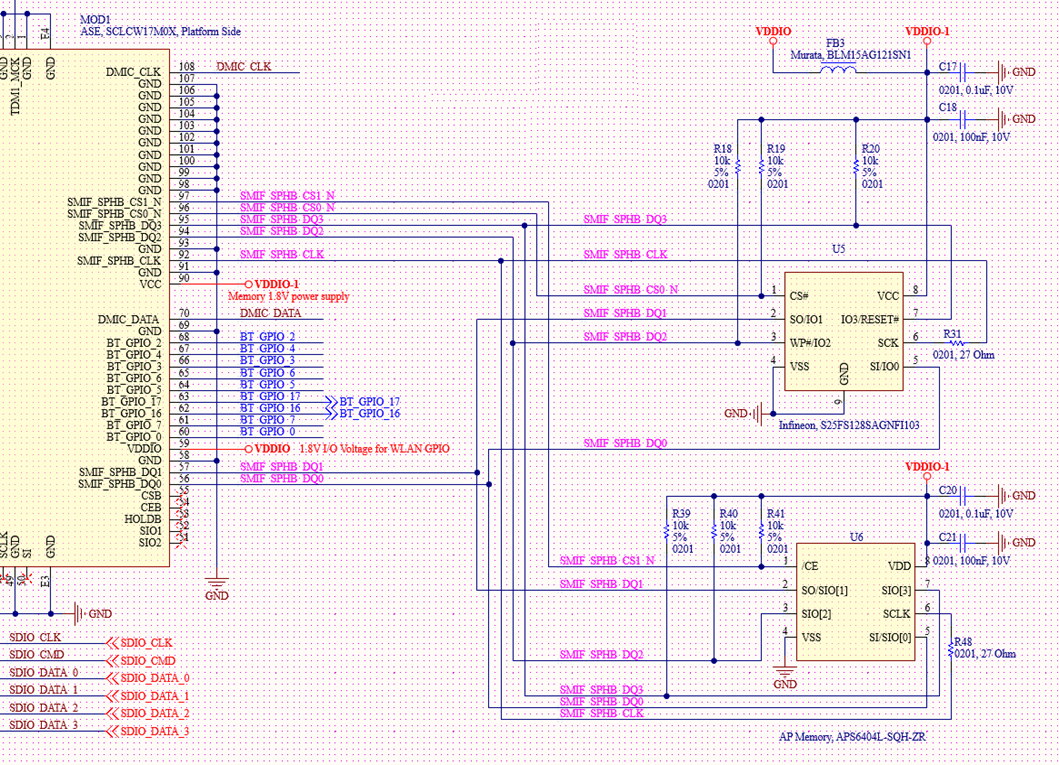

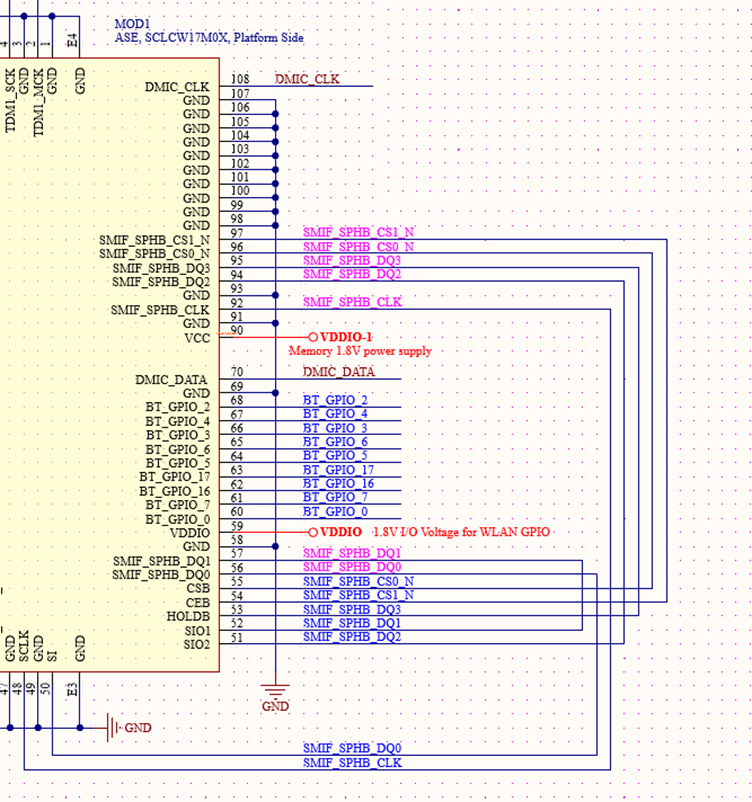

Serial Memory Interface (SMIF) Connection.

For the Veda IF912 without embedded memory variant (453-00396R), user can add external memory (NOR Flash and PSRAM) to the SMIF. Example connections are shown below. Note: VDDIO is limited to 1.8V.

For the Veda IF912 with embedded memory variant (453-00397R), user need to connect SMIF to the embedded memory pin out (pin48/50; pin51 to pin-55). Example connections are shown below.

SDIO and gSPI strapping configuration

SDIO and gSPI in Veda IF912 are muxed together on the same pin out, please reference Pin Out / Package Layout .

A strapping option pin SDIO_DATA[2] is used to configure between SDIO and gSPI. Default is in “H” state which is SDIO mode. Pull this pin to “L” will be set in gSPI mode.

SDIO mode

Veda IF912 provide support for SDIO V 3.0, including the new UHS-I modes:

- DS: Default speed (DS) up to 25 MHz, including 1 and 4-bit modes (1.8 V signaling

- HS: High-speed up to 50 MHz (1.8 V signaling)

- SDR12: SDR up to 25 MHz (1.8 V signaling)

- SDR25: SDR up to 50 MHz (1.8 V signaling)

- SDR50: SDR up to 100 MHz (1.8 V signaling)

- DDR50: DDR up to 50 MHz (1.8 V signaling)

Notes:

- The UHS-1 rate SDR104, that is part of the SDIO V 3.0 specification, is not supported.

- Veda IF912 is backward compatible with SDIO V 2.0 host interfaces. Note however that it can only support 1.8 V signaling. It cannot support 3.3 V signaling during initialization post power cycle and in default/high speed SDIO V 2.0 modes. The host must use 1.8 V signaling.

- According to the SDIO specification, pull-ups in the 10 kΩ to 100 kΩ range are required on the four DATA lines and the CMD line. This requirement must be met during all operating states either through the use of external pull-up resistors or through proper programming of the SDIO host’s internal pull-ups.

gSPI mode

Veda IF912 has the option of using the simplified generic SPI (gSPI) interface/protocol.

Characteristics of the gSPI mode include:

- Up to 50-MHz operation

- Fixed delays for responses and data from the device

- Alignment to host gSPI frames (16 or 32 bits)

- Up to 2-KB frame size per transfer

- Little-endian and big-endian configurations

- A configurable active edge for shifting

- Packet transfer for CCM/CP Traffic/Data Exchange

Note: gSPI mode is enabled using the strapping option pins.

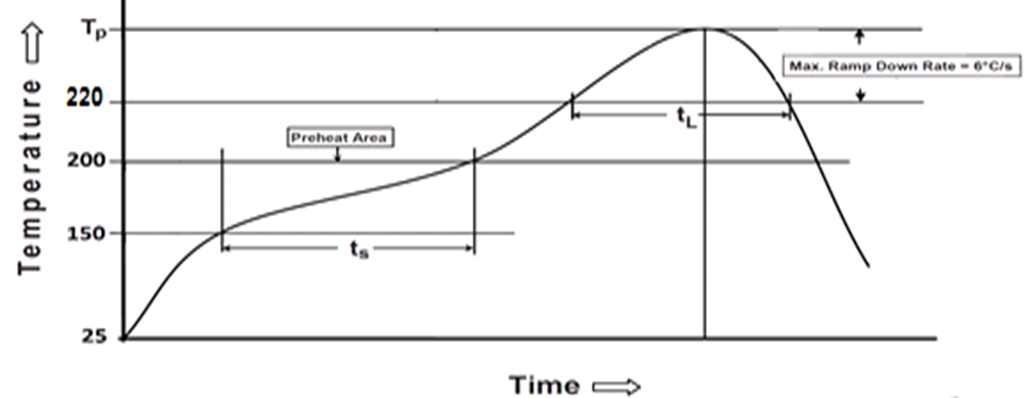

Surface Mount Conditions

The following soldering conditions are recommended to ensure device quality.

Recommended Stencil Aperture

TBD

Note: The stencil thickness is 0.12mm.

Soldering

Note: When soldering, the stencil thickness should be 0.12 mm.

Convection reflow or IR/Convection reflow (one-time soldering or two-time soldering in air or nitrogen environment)

Measuring point – IC package surface

Temperature profile:

- Solder paste alloy: SAC305(Sn96.5 / Ag3.0 / Cu 0.5)

- Pre-heat temperature: 150℃ ~ 200℃; Soak time: 60 second ~ 120 second

- Peak temperature: 235℃ ~ 250℃

- Time above 220℃: 40 second ~ 90 second

- Optimal cooling rate < 3℃/second

- The oxygen concentration < 2000 ppm

Application Note for Surface Mount Modules

Introduction

Shipping and Labeling

Reflow Parameters

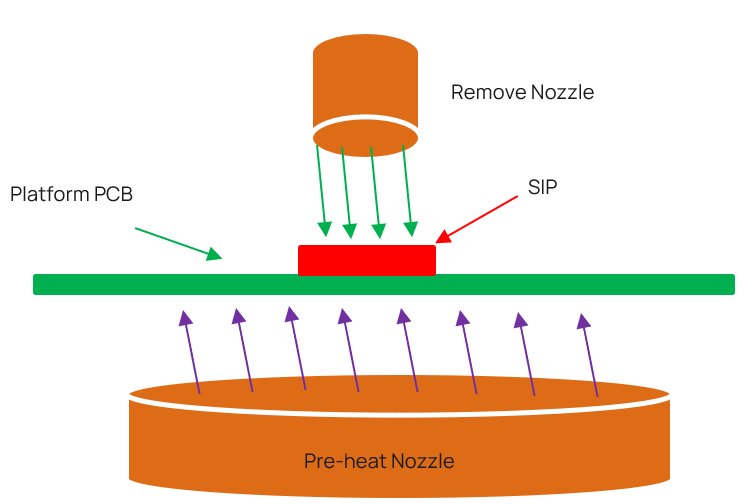

Cautions when Removing the SIP from the Platform for RMA

- Bake the platform PCBA before removing the Veda IF912 module from the platform.

- Remove the Vedaa IF912 module by using a hot air gun. This process should be carried out by a skilled technician.

Recommended conditions for one-side component platform:

- Set the hot plate at 280°C.

- Put the platform on the hot plate for 8~10 seconds.

- Remove the device from platform.

Recommended conditions for two-side components platform:

- Use two hot air guns.

- On the bottom, use a pre-heated nozzle (temp setting of 200~250°C) at a suitable distance from the platform PCB.

On the top, apply a remove nozzle (temp setting of 330°C). Heat until device can be removed from platform PCB.

- Remove the residue solder under the bottom side of device. (Note: Alternate module pictured as an example)

|  |

| (Not accepted for RMA) | (Accepted for RMA analysis) |

- Remove and clean the residue flux as needed.

Precautions for Use:

- Opening/handling/removing must be done on an anti-ESD treated workbench. All workers must also have undergone anti-ESD treatment.

- The devices should be mounted within one year of the date of delivery.

- The Veda IF912 modules are MSL level 4 rated.

Environmental and Reliability

Environmental Requirements

Required Storage Conditions

Prior to Opening the Dry Packing

The following are required storage conditions prior to opening the dry packing:

- Normal temperature: 5~40˚C

- Normal humidity: 80% (Relative humidity) or less

- Storage period: One year or less

Note: Humidity means relative humidity.

After Opening the Dry Packing

The following are required storage conditions after opening the dry packing (to prevent moisture absorption):

Storage conditions for one-time soldering:

- Temperature: 5-25°C

- Humidity: 60% or less

- Period: 72 hours or less after opening

Storage conditions for two-time soldering

Storage conditions following opening and prior to performing the 1st reflow:

- Temperature: 5-25°C

- Humidity: 60% or less

- Period: A hours or less after opening

Storage conditions following completion of the 1st reflow and prior to performing the 2nd reflow

- Temperature: 5-25°C

- Humidity: 60% or less

- Period: B hours or less after completion of the 1st reflow

Note: Should keep A+B within 72 hours.

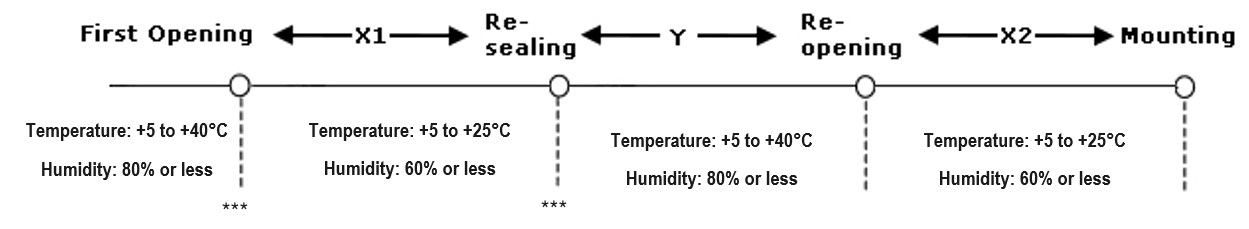

Temporary Storage Requirements after Opening

The following are temporary storage requirements after opening:

- Only re-store the devices once prior to soldering.

- Use a dry box or place desiccant (with a blue humidity indicator) with the devices and perform dry packing again using vacuumed heat-sealing.

The following indicate the required storage period, temperature, and humidity for this temporary storage:

Storage temperature and humidity:

*** - External atmosphere temperature and humidity of the dry packing

Storage period:

- X1+X2 – Refer to Material handling information

- Required Storage Conditions. Keep is X1+X2 within 72 hours.

- Y – Keep within two weeks or less.

Baking Conditions

Baking conditions and processes for the module follow the J-STD-033 standard which includes the following:

- The calculated shelf life in a sealed bag is 12 months at <40℃ and <80% relative humidity.

- Once the packaging is opened, the SiP must be mounted (per MSL4/Moisture Sensitivity Level 4) within 72 hours at <30˚C and <60% relative humidity.

If the SiP is not mounted within 72 hours or if, when the dry pack is opened, the humidity indicator card displays >10% humidity, then the product must be baked for 48 hours at 125 ˚C (±5 ˚C).

Regulatory, Qualification & Certifications

Regulatory Approvals

TBD

Bluetooth SIG Qualification

TBD

Certified Antennas

The Veda IF912 module was tested with antennas listed in the following table. The OEM can choose a different manufacturer’s antenna but must make sure it is of same type and that the gain is less than or equal to the antenna that is approved for use.

| Manufacturer | Model | Ezurio Part Number | Type | Connector | Peak Gain (dBi) @ 2.4GHz | Peak Gain (dBi) @ 5GHz | Peak Gain (dBi) @ 6GHz |

|---|---|---|---|---|---|---|---|

| Ezurio (formerly Laird Connectivity) | FlexMIMO 6E | EFD2471A3S-10MH4L | PIFA | MHF4L | 2.2 | 3.8 | 3.3 |

| Ezurio (formerly Laird Connectivity) | FlexPIFA 6E | EFB2471A3S-10MH4L | PIFA | MHF4L | 2.2 | 3.9 | 3.8 |

| Ezurio (formerly Laird Connectivity) | Mini NanoBlade Flex 6 GHz | EMF2471A3S-10MH4L | PCB Dipole | MHF4L | 2.4 | 4.4 | 5.2 |

| Joymax Electronics | Dipole 6E | TWX-100BRSAX-2001 / TWX-100BRS3B | Dipole | RP-SMA | 2 | 4.0 | 4.0 |

| Yageo (Pulse) | ANT1608LL14R2460A | Chip Antenna | 2.3 | 2.7 | 3.3 |

Ordering Information

| Part Number | Description |

|---|---|

| 453-00396R | Module, Veda IF912, SIP, Dual Band, No Embedded Memory, RF Trace Pin, Tape and Reel |

| 453-00396C | Module, Veda IF912, SIP, Dual Band, No Embedded Memory, RF Trace Pin, Cut Tape |

| 453-00397R | Module, Veda IF912, SIP, Dual Band, Embedded Memory, 8M PSRAM, 8M Flash, RF Trace Pin, Tape and Reel |

| 453-00397C | Module, Veda IF912, SIP, Dual Band, Embedded Memory, 8M PSRAM, 8M Flash, RF Trace Pin, Cut Tape |

| 453-00396-K1 | Development Kit, Module, Veda IF912, SIP, Dual Band, External Memory, RF Trace Pin |

Legacy - Revision History

| Version | Date | Notes | Contributors | Approver |

|---|---|---|---|---|

| 0.1 | 13 May 2025 | Preliminary release | Andrew Chen | Andy Ross |

| 0.2 | 22 May 2025 | Section 4: Update Storage humidity range to 5%~95%. Operating humidity range <85%. Section 6: Update the SDIO/gSPI pin details. Section 7.2: Correct the schematic drawing on SMIF connection (Chip select pin) with external NOR and PSRAM. | Andrew Chen | Andy Ross |

| 0.3 | 20 June 2025 | Correct the pin define on pin 82-83 | Andrew Chen | Andy Ross |

| 0.4 | 14 July 2025 | Update RF performance | Andrew Chen | Andy Ross |

| 0.5 | 16 Sep 2025 | Corrected to reflect that Bluetooth does not support BR/EDR | Andrew Chen | Andy Ross |

| 0.6 | 2025/10/09 | Add Pin-108: DMIC_CLK | Andrew Chen | Andy Ross |

| 0.7 | 2025/12/10 | On section 6: Add the module pin out mapping to IFX main chip pin out | Andrew Chen | Andy Ross |

/filters:background_color(white)/2025-07/IF9121.png)